Wësst Dir wéi Dir den EMI Problem léist wann Dir Multi-Layer PCB Design?

Loosst mech Iech soen!

Et gi vill Weeër fir EMI Probleemer ze léisen.Modern EMI Ënnerdréckungsmethoden enthalen: EMI Ënnerdréckungsbeschichtung benotzen, passenden EMI Ënnerdréckungsdeeler auswielen an EMI Simulatiounsdesign.Baséiert op de meeschte Basis PCB Layout, diskutéiert dësem Pabeier d'Funktioun vun PCB Stack am Kontroll EMI Stralung an PCB Design Kompetenzen.

Muecht Bus

Den Ausgangsspannungssprang vum IC ka beschleunegt ginn andeems en entspriechend Kapazitéit no beim Power Pin vum IC plazéiert.Allerdéngs ass dëst net d'Enn vum Problem.Wéinst der limitéierter Frequenzreaktioun vum Kondensator ass et onméiglech fir de Kondensator déi harmonesch Kraaft ze generéieren déi néideg ass fir den IC Output propper an der voller Frequenzband ze féieren.Zousätzlech wäert d'transient Spannung, déi um Stroumbus geformt gëtt, Spannungsfall op béide Enden vun der Induktioun vum Ofkupplungswee verursaachen.Dës transient Spannungen sinn den Haapt gemeinsame Modus EMI Interferenzquellen.Wéi kënne mir dës Problemer léisen?

Am Fall vun IC op eisem Circuit Board kann d'Kraaftschicht ronderëm den IC als e gudden Héichfrequenzkondensator ugesi ginn, deen d'Energie sammele kann, déi vum diskrete Kondensator geleckt gëtt, deen héichfrequenz Energie fir propper Ausgang liwwert.Zousätzlech ass d'Induktioun vun enger gudder Kraaftschicht kleng, sou datt de transiente Signal dat vum Induktor synthetiséiert ass och kleng ass, sou datt de gemeinsame Modus EMI reduzéiert gëtt.

Natierlech muss d'Verbindung tëscht der Stroumversuergungsschicht an dem IC Stroumversuergungspin esou kuerz wéi méiglech sinn, well de Risingrand vum digitale Signal méi séier a méi séier ass.Et ass besser et direkt un de Pad ze verbannen, wou den IC Power Pin läit, wat separat diskutéiert muss ginn.

Fir de gemeinsame Modus EMI ze kontrolléieren, muss d'Kraaftschicht e gutt entworf Pair vu Kraaftschichten sinn fir ze hëllefen ze entkoppelen an eng genuch niddereg Induktioun ze hunn.Verschidde Leit kënnen froen, wéi gutt ass et?D'Äntwert hänkt vun der Kraaftschicht, dem Material tëscht de Schichten an der Operatiounsfrequenz of (dh eng Funktioun vun der IC-Steigerzäit).Am Allgemengen ass d'Distanz vu Kraaftschichten 6mil, an d'Interlayer ass FR4 Material, sou datt déi gläichwäerteg Kapazitéit pro Quadratzoll Kraaftschicht ongeféier 75pF ass.Natierlech, wat méi kleng d'Schichtabstand ass, dest méi grouss d'Kapazitéit.

Et ginn net vill Apparater mat enger Opstiegzäit vun 100-300ps, awer no der aktueller Entwécklungsquote vum IC wäerten d'Apparater mat der Opstiegzäit am Beräich vun 100-300ps en héijen Undeel besetzen.Fir Circuiten mat 100 bis 300 PS Opstiegszäiten, ass 3 Mill Layer Abstand net méi uwendbar fir déi meescht Uwendungen.Zu där Zäit ass et néideg d'Delaminatiounstechnologie mat der Interlayer Abstand manner wéi 1mil ze adoptéieren, an d'FR4 dielektrescht Material mat dem Material mat héijer dielektresche Konstant ze ersetzen.Elo kënnen Keramik a Pottplastik den Designfuerderunge vun 100 bis 300ps Opstiegzäitkreesser entspriechen.

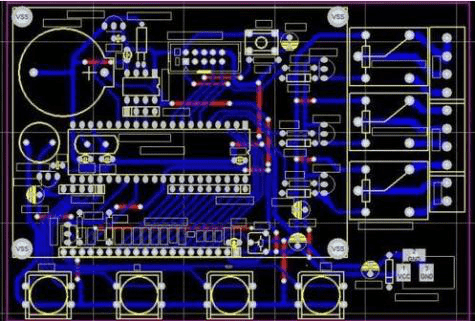

Och wann nei Materialien a Methoden an Zukunft benotzt kënne ginn, sinn allgemeng 1 bis 3 ns Opstiegzäitkreesser, 3 bis 6 Mill Schichtabstand, an FR4 dielektresch Materialien normalerweis genuch fir High-End Harmoniken ze handhaben an transient Signaler niddereg genuch ze maachen, dat ass , Gemeinsam Modus EMI kann ganz niddereg reduzéiert ginn.An dësem Pabeier gëtt den Design Beispill vun PCB layered stacking ginn, an der Layer Abstand ugeholl 3 ze 6 mil.

elektromagnetesch Schirmung

Vun der Signal Routing Siicht soll eng gutt Layer Strategie ginn all Signal Spure an een oder méi Schichten ze Plaz, déi nieft der Muecht Layer oder Buedem Fliger sinn.Fir Stroumversuergung soll eng gutt Layerstrategie sinn datt d'Kraaftschicht nieft dem Buedemplang ass, an d'Distanz tëscht der Kraaftschicht an dem Buedemplang soll sou kleng wéi méiglech sinn, dat ass wat mir d'"Layer" Strategie nennen.

PCB Stack

Wéi eng Stackingstrategie kann hëllefen EMI ze schützen an z'ënnerdrécken?Déi folgend Layer Stacking Schema gëtt ugeholl datt d'Energieversuergungsstroum op enger eenzeger Schicht fléisst an datt eenzel Spannungen oder Multiple Spannungen a verschiddenen Deeler vun der selwechter Schicht verdeelt ginn.De Fall vu Multiple Power Schichten gëtt spéider diskutéiert.

4-Ply Plack

Et ginn e puer potenziell Problemer am Design vu 4-Ply Laminaten.Éischtens, och wann d'Signalschicht an der äusserer Schicht ass an d'Kraaft an d'Buedemfläch an der banneschter Schicht sinn, ass d'Distanz tëscht der Kraaftschicht an der Grondfläch nach ëmmer ze grouss.

Wann d'Käschtefuerderung déi éischt ass, kënnen déi folgend zwou Alternativen zum traditionelle 4-Ply Board considéréiert ginn.Béid vun hinnen kënnen d'EMI Ënnerdréckungsleistung verbesseren, awer si sinn nëmme gëeegent fir de Fall wou d'Dicht vun de Komponenten um Bord niddereg genuch ass an et genuch Gebitt ronderëm d'Komponenten ass (fir déi erfuerderlech Kupferbeschichtung fir d'Energieversuergung ze placéieren).

Déi éischt ass de bevorzugt Schema.Déi baussenzeg Schichten vun PCB sinn all Schichten, an der Mëtt zwou Schichten sinn Signal / Muecht Schichten.D'Energieversuergung op d'Signalschicht gëtt mat breet Linnen geréckelt, wat de Weeimpedanz vun der Stroumversuergungsstroum niddereg mécht an d'Impedanz vum Signalmikrostrip Wee niddereg.Aus der Perspektiv vun der EMI Kontroll ass dëst déi bescht 4-Schicht PCB Struktur verfügbar.Am zweete Schema dréit déi baussenzeg Schicht d'Kraaft an d'Buedem, an d'Mëtt zwou Schicht dréit d'Signal.Am Verglach mat der traditioneller 4-Layer Board ass d'Verbesserung vun dësem Schema méi kleng, an d'Interlayer Impedanz ass net sou gutt wéi déi vun der traditioneller 4-Layer Board.

Wann d'Verdrahtungsimpedanz kontrolléiert gëtt, sollt de uewe genannte Stackschema ganz virsiichteg sinn fir d'Verdrahtung ënner der Kupferinsel vun der Energieversuergung a vum Buedem ze leeën.Zousätzlech soll d'Kupferinsel op der Stroumversuergung oder Stratum sou vill wéi méiglech matenee verbonne sinn fir d'Konnektivitéit tëscht DC an der niddereger Frequenz ze garantéieren.

6-Ply Plack

Wann d'Dicht vun de Komponenten op der 4-Schichtplatte grouss ass, ass d'6-Schichtplack besser.Allerdéngs ass de shielding Effekt vun e puer stacking Schemaen am Design vun 6-Layer Bord net gutt genuch, an der transient Signal vun Muecht Bus ass net reduzéiert.Zwee Beispiller ginn ënnert diskutéiert.

Am éischte Fall sinn d'Energieversuergung an d'Buedem an der zweeter a fënnefter Schichten plazéiert.Wéinst der héijer Impedanz vu Kupferbekleeder Energieversuergung ass et ganz ongënschteg fir d'gemeinsame Modus EMI Stralung ze kontrolléieren.Wéi och ëmmer, aus der Siicht vun der Signalimpedanzkontroll ass dës Method ganz korrekt.

Am zweete Beispill sinn d'Energieversuergung an d'Buedem an der drëtter a véierter Schichten plazéiert.Dësen Design léist de Problem vun der Kupferbekleeder Impedanz vun der Energieversuergung.Wéinst der schlechter elektromagnetescher Schirmleistung vun der Schicht 1 a Schicht 6 erhéicht den Differentialmodus EMI.Wann d'Zuel vun de Signallinnen op den zwou baussenzege Schichten am mannsten ass an d'Längt vun de Linnen ganz kuerz ass (manner wéi 1 / 20 vun der héchster harmonescher Wellelängt vum Signal), kann den Design de Problem vum Differentialmodus EMI léisen.D'Resultater weisen datt d'Ënnerdréckung vum Differentialmodus EMI besonnesch gutt ass wann déi baussenzeg Schicht mat Kupfer gefüllt ass an d'Kupferbekleedungsgebitt gegrënnt ass (all 1 / 20 Wellelängtintervall).Wéi uewen ernimmt, Koffer soll geluecht ginn

Post Zäit: Jul-29-2020